Components and Parts Idea/Ad Exchange, free for members. > Southwest

> Farm Agri

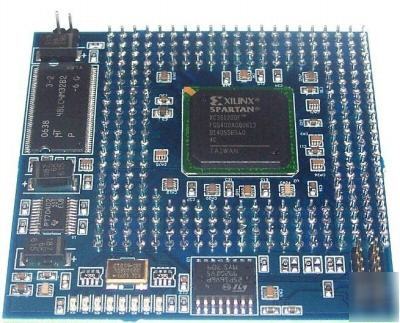

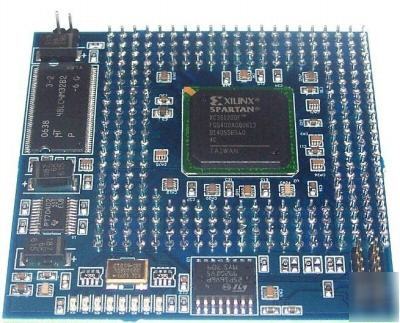

> DARNAW1 pga module with spartantm-3E XC3S1200E

DARNAW1 pga module with spartantm-3E XC3S1200E

Our Darnaw1 release is a module using SpartanTM-3E XC3S1200E. Darnaw1 is a PGA style module allowing the use of the latest XilinxTM SpartanTM-3E FPGA in low technology PCB, prototype or wire wrap boards.

PGA_I/O - 219 FPGA user I/O available. 3 of the 4 bank voltages are set by user wiring. (2.5V and 1.2V available as outputs from on-board regulators, 3,3V is the input supply). 10 pins for FPGA and SPI programming supporting in target programming. Power supplies and bank voltages - 33 pins. No-connects - 11 pins.

It also is possible to operate the Darnaw1 in a reduced pinout with only the outer and inner pins of the PGA used. This configuration gives enough power pins to operate and 110 I/O and can make connections to the PGA much simpler on your target. (Note that some pins in the mid rows are used for in target programming features. This does not affect JTAG/SPI header operation on the Darnaw1 itself.)

Flash Memory (configuration + storage) - 16Mbit SPI Flash. Usually a ST Microelectronics M25P16 but may vary from batch to batch.

SDRAM - 128Mbit in 8Mx32 configuration. Usually a Micron MT48LC4M32B2 fitted but may vary from batch to batch.

Oscillator - Usually 32MHz 7x5 oscillator will be fitted. Occasionally we make vary this based on part availability.

Input Power Supply - Notional single 3.3V input only needed. On board regulators for 2.5V and 1.2V.

Bank Voltages - Banks 0,1,2 are set by host by connecting suitable power to appropriate PGA pins. 2.5V is available as an output on PGA pins and can be used for variable bank voltages. Bank3 is fixed at 3.3V.

SPI/JTAG - Separate SPI and JTAG programming headers are implemented. There is also a jumper to hold FPGA in pre-configuration state.